- 您现在的位置:买卖IC网 > Sheet目录3889 > PIC16F1827-I/SS (Microchip Technology)IC PIC MCU FLASH 4K 20-SSOP

205

2570N–AVR–05/11

ATmega325/3250/645/6450

with Auto triggering from a source other than the ADC Conversion Complete, each conversion

will require 25 ADC clocks. This is because the ADC must be disabled and re-enabled after

every conversion.

In Free Running mode, a new conversion will be started immediately after the conversion com-

pletes, while ADSC remains high. For a summary of conversion times, see Table 23-1.

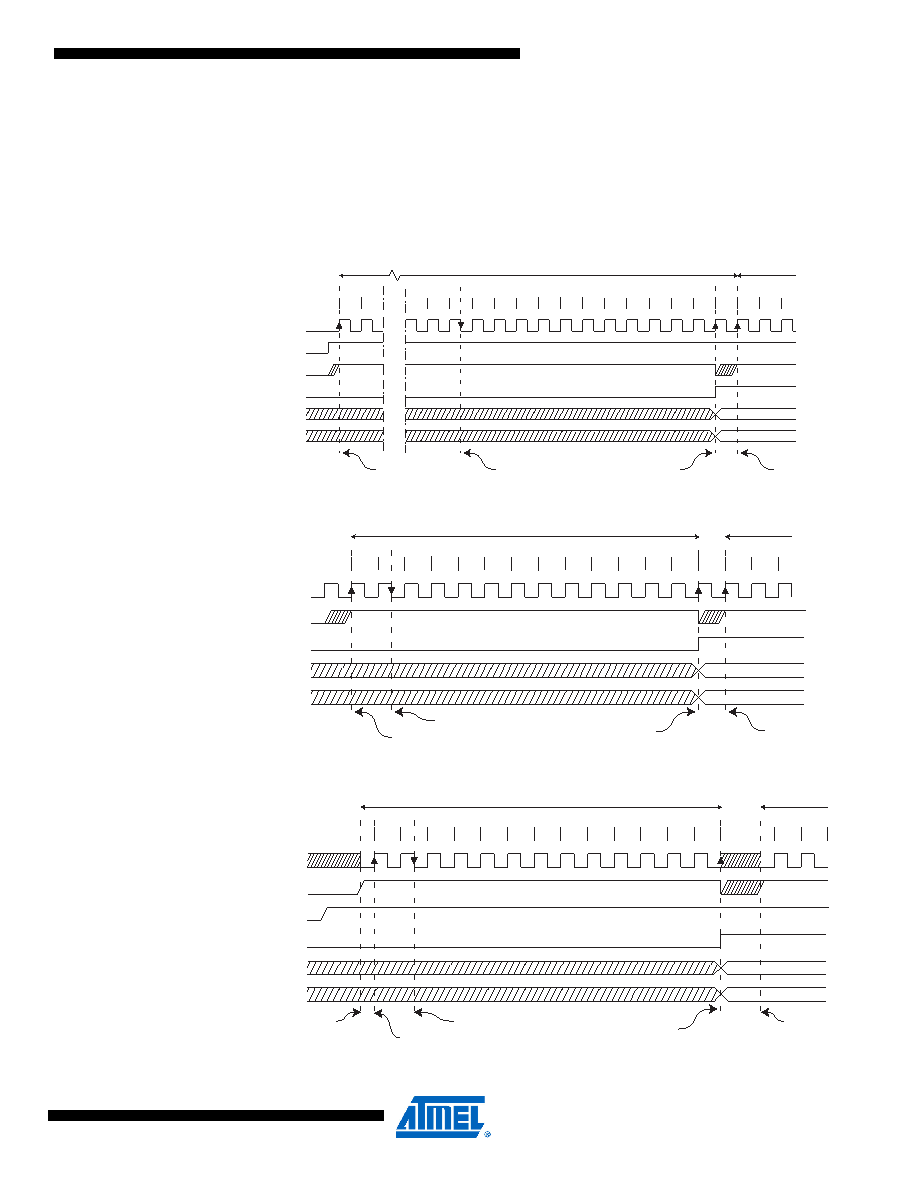

Figure 23-4. ADC Timing Diagram, First Conversion (Single Conversion Mode)

Figure 23-5. ADC Timing Diagram, Single Conversion

Figure 23-6. ADC Timing Diagram, Auto Triggered Conversion

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

Sample & Hold

ADIF

ADCH

ADCL

Cycle Number

ADEN

1

212

13

14

15

16

17

18

19

20

21

22

23

24

25

1

2

First Conversion

Next

Conversion

3

MUX and REFS

Update

MUX and REFS

Update

Conversion

Complete

1

2

3

4

5

6

7

8

9

10

11

12

13

Sign and MSB of Result

LSB of Result

ADC Clock

ADSC

ADIF

ADCH

ADCL

Cycle Number

12

One Conversion

Next Conversion

3

Sample & Hold

MUX and REFS

Update

Conversion

Complete

MUX and REFS

Update

1

2

3

4

5

6

7

8

9

10

11

12

13

Sign and MSB of Result

LSB of Result

ADC Clock

Trigger

Source

ADIF

ADCH

ADCL

Cycle Number

12

One Conversion

Next Conversion

Conversion

Complete

Prescaler

Reset

ADATE

Prescaler

Reset

Sample &

Hold

MUX and REFS

Update

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC12C508-04/P

IC MCU OTP 512X12 8DIP

22-15-3153

CONN FFC/FPC 15POS .100 RT ANG

PIC16F1826-I/MV

IC PIC MCU FLASH 2K 28-UQFN

PIC16F1825-I/P

MCU PIC 14K FLASH 1K RAM 14DIP

22-02-3153

CONN FFC/FPC VERTICAL 15POS .100

22-15-3143

CONN FFC/FPC 14POS .100 RT ANG

22-02-3143

CONN FFC/FPC VERTICAL 14POS .100

502078-2110

CONN FPC .25MM 21POS R/A SMD

相关代理商/技术参数

PIC16F1827T-I/ML

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/MQ

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/MV

功能描述:8位微控制器 -MCU 7KB Flash 384 RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/SO

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1827T-I/SS

功能描述:8位微控制器 -MCU 7KB Flash 384 byte 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1828-E/ML

功能描述:8位微控制器 -MCU 7 KB Flash 256b RAM 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1828-E/P

功能描述:8位微控制器 -MCU 7 KB Flash 256b RAM 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1828-E/SO

功能描述:8位微控制器 -MCU 7 KB Flash 256b RAM 32 MHz Int. Osc RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT